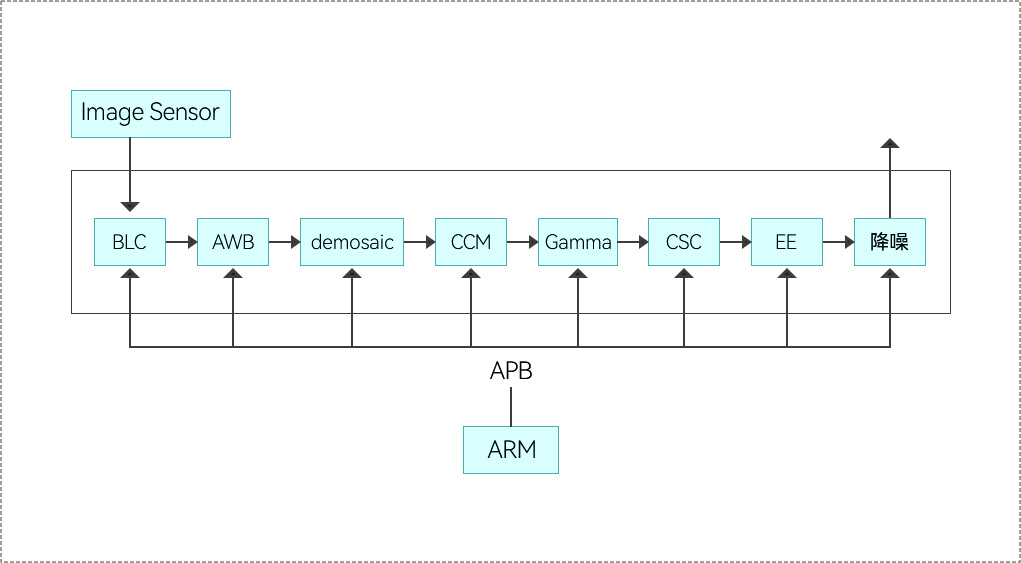

ISP IP Core 通过APB总线用于控制寄存器,支持 UltraScale+ / Zynq UltraScale+ 系列 FPGA 器件

ISP IP Core 为您提供了快速可靠、更低成本和更高性能的解决方案,显著缩短上市时间,适用于高清图像视频处理、智能视觉的场景,如医疗内窥镜、手术机器人、工业相机、汽车自动驾驶、无人机、机器人、AR/VR、智慧城市、智能交通、安防监控等领域

每时钟周期处理1个像素,最高频率 300Mhz

APB 总线控制寄存器,比 AXI Lite 总线 更省资源

低延时,采用行缓存,延时微秒级

最大分辨率支持 4096x2048

可灵活组合各个模块

FPGA Vivado、Verilog 代码解决方案

ISP 是一种专门用于处理图像信号的技术,可以对从图像传感器获取的原始数据进行处理。ISP 结合ARM处理器的图像信号处理系统,使用 APB 控制寄存器,控制黑电平校正(BLC)、自动白平衡(AWB)、去马赛克(demosaic)、颜色矫正矩阵(CCM)、Gamma 矫正、颜色空间转换(CSC)、边沿增强(EE)、2D 降噪等模块,灵活组合。

设计语言

Verilog

开发工具

Vivado 2020.1

支持器件

AMD Virtex Ultrascale+/Kintex UltraScale+/Artix UltraScale+ 系列

AMD Zynq UltraScale+ MPSoC/Zynq UltraScale+ RFSoC 系列

IP 资源消耗评估采用 AMD Zynq UltraScale+ MPSoC 系列 FPGA 开发板,提供了一个功能齐全的设计平台,用于构建数据存储加速应用。Zynq UltraScale+ MPSoC XCZU5EV FPGA 开发板提供了一个带有参考设计的开箱即用型硬件平台,可缩短开发时间,让您专注于目标应用。

器件系列

Zynq UltraScale+ MPSoC

芯片型号

XCZU5EV-2SFVC784I

频率 (MHz)

300

CLB Regs

22161

CLB LUTs

18541

CLB

3969

BRAM Tile

33

Design Tools

Vivado 2020.1

注:IP 实际逻辑资源消耗受实例化中其他逻辑资源消耗影响

ISP FPGA IP Core 主要适用于高清图像视频处理、智能视觉的场景,如医疗内窥镜、手术机器人、工业相机、汽车自动驾驶、无人机、机器人、AR/VR、智慧城市、智能交通、安防监控等领域的场景。

医疗内窥镜、手术机器人

工业视觉

机器人、无人机

汽车自动驾驶

智慧城市交通

安防监控

请您补充以下信息,开启一键下载。