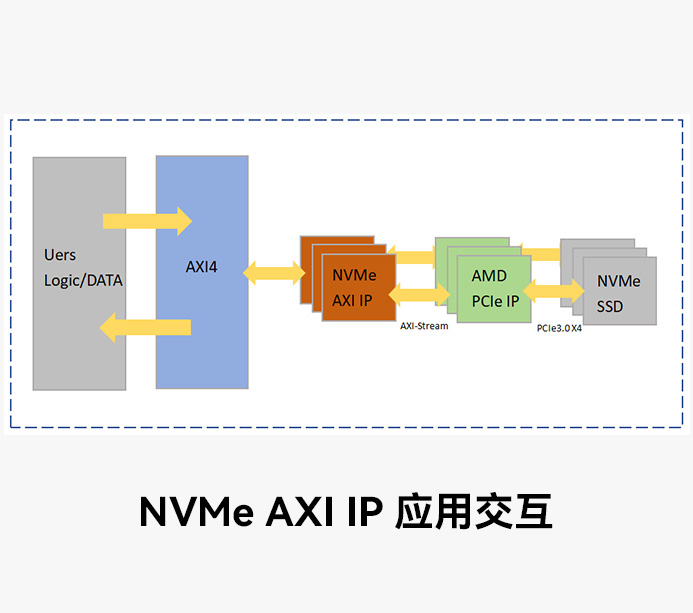

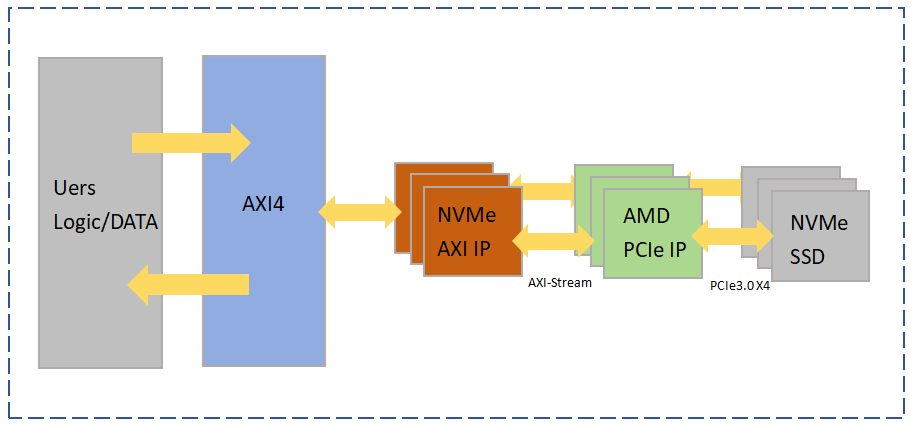

NVMe AXI FPGA IP Core 通过 AXI4 总线协议标准接口进行交互并且内部实现 PCIe Bridge,支持 AXI Master FULL 和 AXI Stream 两个版本;通过 RC/RQ/CC/CQ AXI Stream 接口与 AMD Devices PCI Express IP 集成内核进行交互,实现不依靠 CPU 对外部存储器 NVMe M.2 SSD 进行读写,兼容 NVM Express 1.4 协议,支持 PCIe Gen 1.0,2.0,3.0,4.0。

NVMe AXI FPGA IP Core 支持 AMD/Xilinx Zynq UltraScale+ RFSoC, Zynq UltraScale+ MPSoC, Virtex UltraScale+, Kintex UltraScale+, Artix UltraScale+, Virtex UltraScale, Kintex UltraScale, Virtex 7 系列 FPGA 器件,为您提供低 FPGA 资源占用、快速可靠、更低成本、高读/写带宽和性能可扩展的解决方案,显著缩短上市时间,满足嵌入式系统对使用 SSD 的需求。适用于高带宽读写、高速数据存储、高扩展的场景,如数据中心及云计算存储、边缘计算、AI智能、企业存储、高速模拟数字信号数据采集存储 、航空航天数据采集存储、自动驾驶车辆采集数据记录和回放、汽车/医疗/工业测试设备、高速雷达/摄像头数据采集存储、以太网 TCP/UDP 网络数据包捕获等领域。

通过 AMD Devices PCI Express IP 内核读写 NVMe M.2 SSD

高带宽,扩展性强,满足嵌入式系统对 SSD 使用需求

支持 AXI FULL 和 AXI Master Stream 两个版本,适合多种应用场景

使用 AMD PCIe IP 硬核模块,支持 PCIe Gen 1.0,2.0,3.0,4.0

基于 PCIe Gen3 X4 读写速率均可达到 3000MB/s

支持最大每个队列 65535 I/O 命令

Verilog 代码解决方案

开发工具

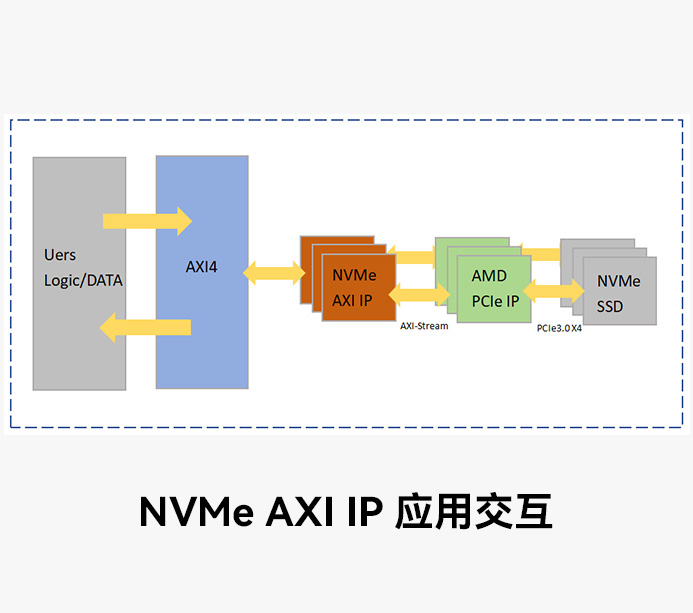

NVMe AXI IP Core 通过 AXI4 总线协议标准接口进行交互并且内部实现了 PCIe Bridge,通过 RC/RQ/CC/CQ AXI Stream 接口与 AMD UltraScale+ Devices Integrated Block for PCIExpress IP 进行交互,实现不依靠 CPU 对外部存储器 NVMe M.2 SSD 进行读写。

有关 AMD UltraScale+ Devices Integrated Block for PCIExpress IP 的详细信息参照 PG213 文档

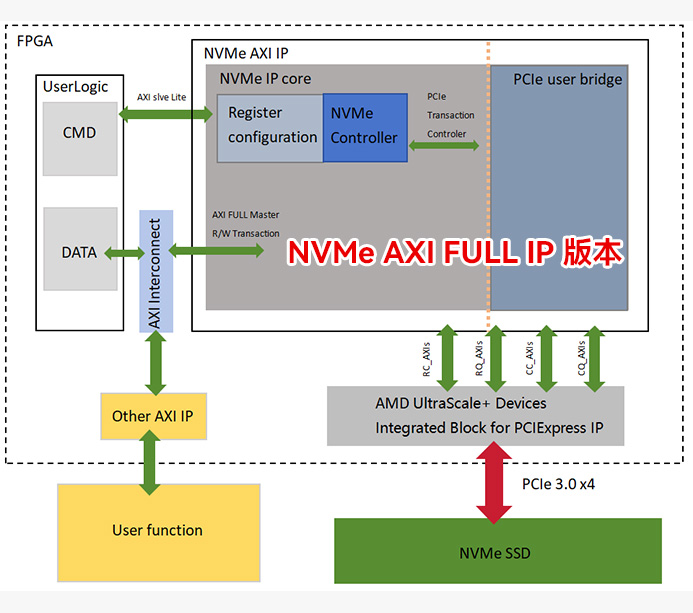

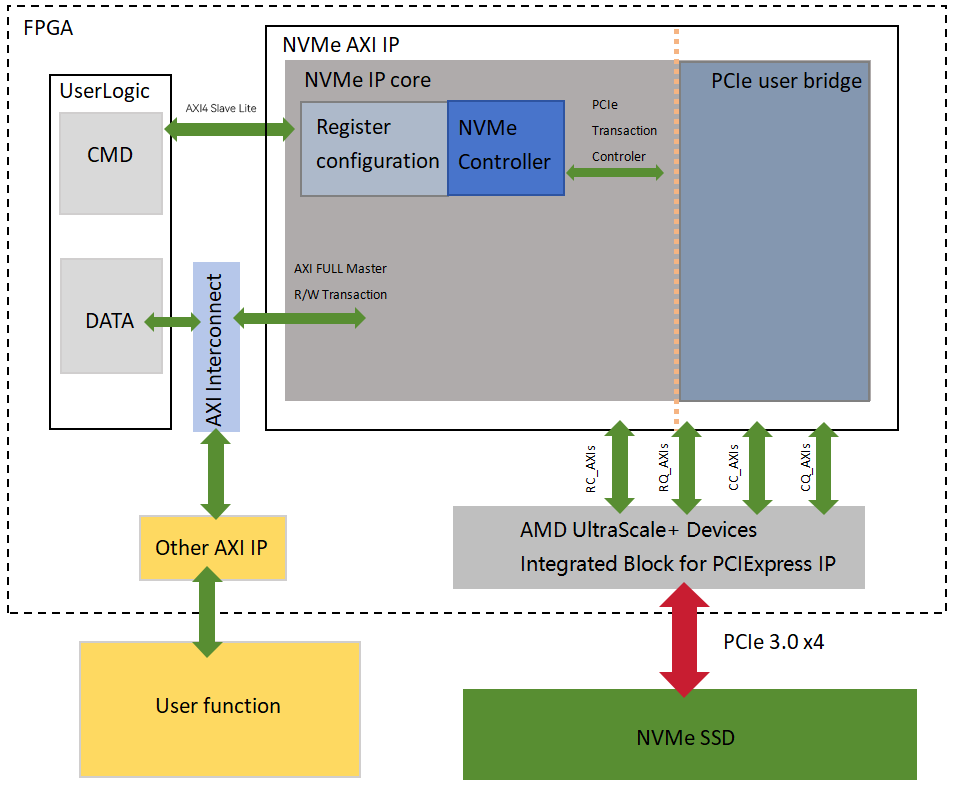

AXI 读写:时钟信号有效并且复位信号拉低,NVMe AXI IP Core 开始进行自动初始化,初始化完成链路打通后,用户的数据流通过 AXI Interconnect IP 写入到 NVMe AXI IP Core 的 AXI Master FULL 接口中进行 NVMe 协议的队列管理门铃逻辑交互,并组成 TLP 层 PCIe 包通过 RC/RQ/CC/CQ AXI Stream 接口与 AMD UltraScale+ Devices Integrated Block for PCIExpress IP 进行连接并输出数据到 NVMe SSD 进行存储。NVMe AXI IP Core 通过 RC/RQ/CC/CQ AXI Stream 接口从 NVMe SSD 中读出数据并通过 AXI Master FULL 接口连接 AXI Interconnect IP 输出给任意 AXI4 标准总线的 IP 进行用户逻辑实现。

NVMe AXI FULL IP 版本框图

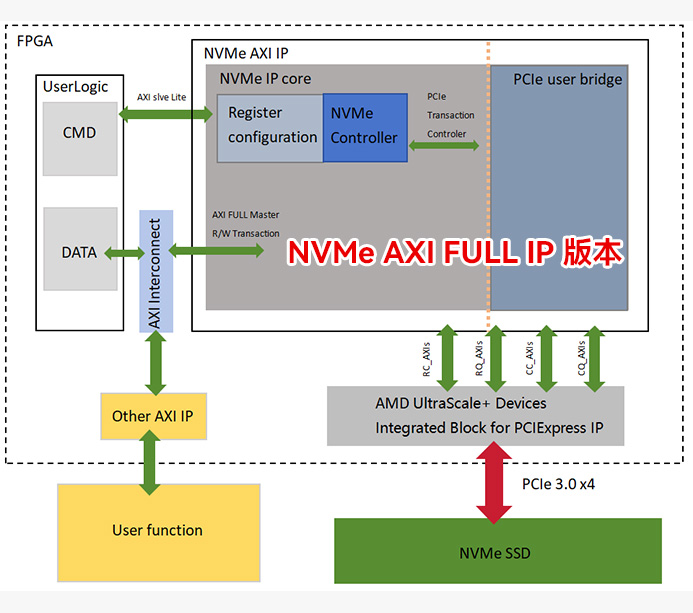

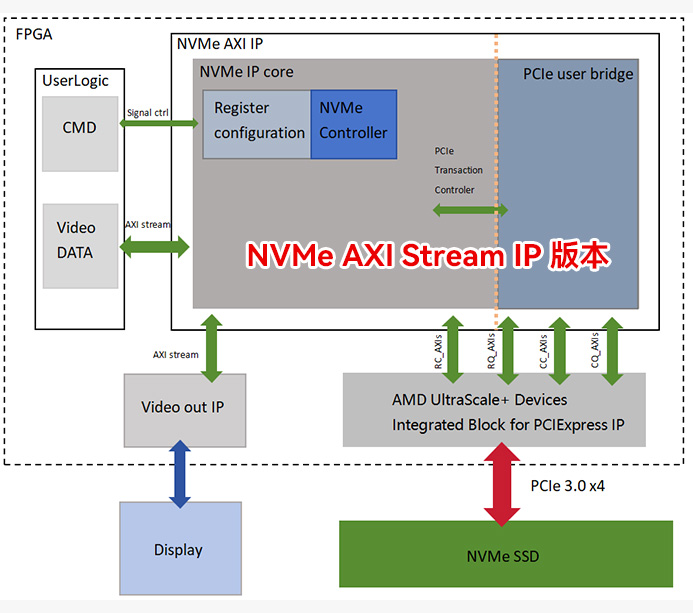

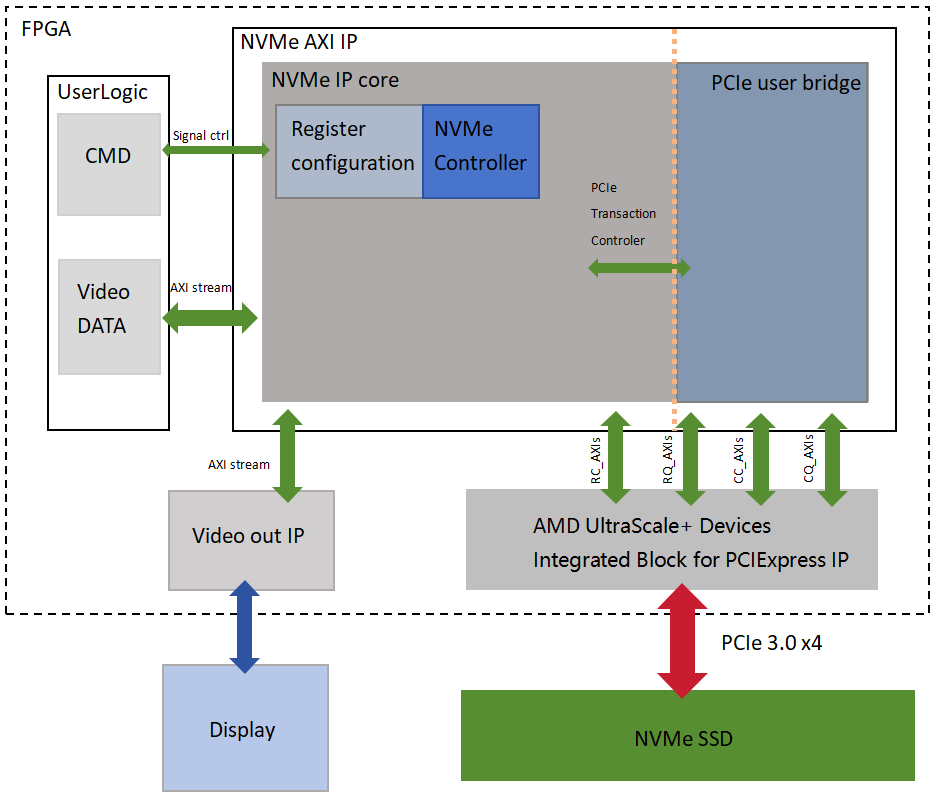

AXI Stream 读写:时钟信号有效并且复位信号拉低,NVMe AXI IP Core 开始进行自动初始化,初始化完成链路打通后,用户的数据流通过 AXI Stream 接口写入到 NVMe AXI IP Core 中进行 NVMe 协议的队列管理门铃逻辑交互,并组成 TLP 层 PCIe 包通过 RC/RQ/CC/CQ AXI Stream 接口与 AMD UltraScale+ Devices Integrated Block for PCIExpress IP 进行连接并输出数据到 NVMe SSD 进行存储。NVMe AXI IP Core 通过 RC/RQ/CC/CQ AXI Stream 接口从 NVMe SSD 中读出数据,通过 AXI Stream 接口输出给 video out IP 连接视频接口进行输出显示。

NVMe AXI Stream IP 版本框图

设计语言

Verilog

开发工具

Vivado 2020.1

支持器件

AMD Virtex 7系列

AMD Virtex Ultrascale/Kintex UltraScale 系列

AMD Virtex Ultrascale+/Kintex UltraScale+/Artix UltraScale+ 系列

AMD Zynq UltraScale+ MPSoC/Zynq UltraScale+ RFSoC 系列

IP 资源消耗评估采用 AMD Zynq UltraScale+ MPSoC 系列 FPGA 开发板,提供了一个功能齐全的设计平台,用于构建数据存储加速应用。Zynq UltraScale+ MPSoC XCZU19EG 开发板提供了一个带有参考设计的开箱即用型硬件平台,可缩短开发时间,让您专注于目标应用。

器件系列

Zynq UltraScale+ MPSoC

芯片型号

XCZU19EG-FFVC1760-2-I

频率 (MHz)

250

CLB Regs

8286

CLB LUTs

8459

CLB

1741

BRAM Tile

5

Design Tools

Vivado 2020.1

注:IP 实际逻辑资源消耗受实例化中其他逻辑资源消耗影响

NVMe AXI Stream/FULL FPGA IP Core 适用于高带宽读写、高速数据存储、高扩展的场景,如数据中心及云计算存储、边缘计算、AI智能、企业存储、高速模拟数字信号数据采集存储 、航空航天数据采集存储、汽车及自动驾数据采集存储及仿真测试、汽车/医疗/工业测试设备、高速雷达/摄像头数据采集存储、以太网 TCP/UDP 网络数据包捕获等领域。

数据中心及云计算存储

汽车自动驾驶数据采集存储与仿真测试

医疗、工业等测试设备

AI、边缘计算、机器学习

网络通信及智能安防监控

航空航天、卫星雷达

请您补充以下信息,开启一键下载。