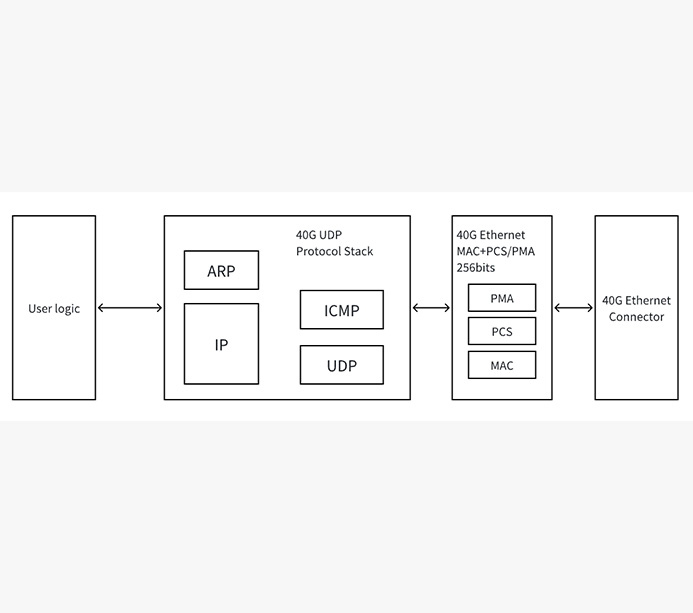

基于 AMD/Xilinx 40G 以太网 MAC IP 开发,MTU 支持高达 9000Bytes 数据传输,标准的 AXI4-Stream 接口,支持 AMD/Xilinx Zynq UltraScale+ RFSoC, Zynq UltraScale+ MPSoC, Zynq 7030/7035/7045/7100, Virtex UltraScale+, Kintex UltraScale+, Artix UltraScale+, Virtex UltraScale, Kintex UltraScale, Virtex 7, Kintex 7 系列 FPGA 器件。40G 万兆以太网以其高带宽和低延迟的特点,能够确保数据的快速传输和实时处理,而 TUDP 协议栈更是提高了数据传输的效率和准确性。

为您提供了快速可靠、更低成本和更高性能的解决方案,显著缩短上市时间,适用于高带宽、低延迟和高速数据传输的场景,如数据中心、科研实验、工业自动化、医疗、测试与测量、4K/8K 高清视频传输、电信、金融交易等领域。

符合 IEEE802.3 标准的 ARP、IPV4、ICMP、UDP 协议栈

快速传输,实时处理,支持 UDP/IP 校验和处理

用户接口和 Ethernet MAC+PCS/PMA IP 接口为标准 AXI4-Stream 接口

ARP 报文应答支持所有查询应答,可缓存 10 ARP 表

MTU 支持 9000Bytes ~ 64Bytes 数据传输

数据总线宽度 256bit,312.5MHz 时钟

Verilog 代码解决方案

开发工具

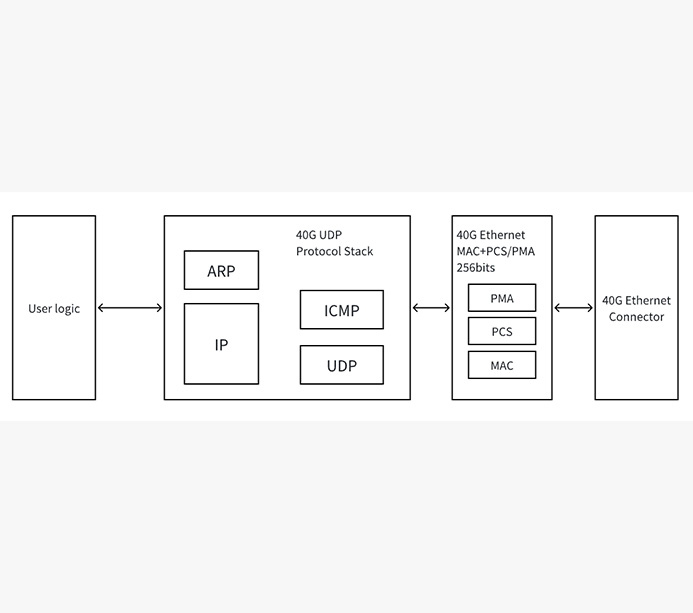

UDP/IP 协议栈 IP Core 与用户接口、Ethernet MAC+PCS/PMA IP 接口均为标准的 AXI4-Stream 接口,其中 Ethernet MAC+PCS/PMA 可以是任何第三方 IP,在提供的设计实例中,使用的是 AMD/Xilinx 40G/50G Ethernet Subsystem IP。

设计语言

Verilog

开发工具

Vivado 2020.1

支持器件

AMD Kintex 7/Virtex 7 系列

AMD Virtex Ultrascale/Kintex UltraScale 系列

AMD Virtex Ultrascale+/Kintex UltraScale+/Artix UltraScale+ 系列

AMD Zynq 7000 SoC 系列 7030/7035/7045/7100

AMD Zynq UltraScale+ MPSoC/Zynq UltraScale+ RFSoC 系列

IP 资源消耗评估采用 AMD Zynq UltraScale+ MPSoC 系列 FPGA 开发板,提供了一个功能齐全的设计平台,用于构建以通信为中心的以太网应用。Zynq UltraScale+ MPSoC XCZU19EG 开发板提供了一个带有参考设计的开箱即用型硬件平台,可缩短开发时间,让您专注于目标应用。

器件系列

Zynq UltraScale+ MPSoC

芯片型号

XCZU19EG-FFVC1760-2-I

频率 (MHz)

312.5

CLB Regs

16324

CLB LUTs

10050

CLB

2478

BRAM Tile

5

URAM

5

Design Tools

Vivado 2020.1

注:IP 实际逻辑资源消耗受实例化中其他逻辑资源消耗影响

40G UDP/IP 协议栈网络加速 FPGA IP Core 主要适用于需要高带宽、低延迟和高速数据传输的场景,如数据中心、科研实验、工业自动化、医疗、测试与测量、4K/8K 高清视频传输、电信、金融交易等领域。

数据中心网络加速及云计算存储

大规模 AI 与机器学习集群

工业自动化及物联网

科研、医疗成像、基因测序

媒体娱乐 4K/8K 高清视频传输

网络通信及金融电信

请您补充以下信息,开启一键下载。